AXI4-Stream to Video Out IPについて

AXI4-Stream to Video Out IPのデータシート#関連資料を読み、必要そうな情報をまとめた。このIPを理解するのが難しく、記事の内容が間違っているかもしれない。間違いは気づき次第修正する。

目次

概要

AXI4-Stream to Video Out IPは、Video Timing Controller(VTC)と組み合わせて使用し、AXI4-Stream I/Fをビデオ信号に変換するIPである。

入出力信号とブロック図

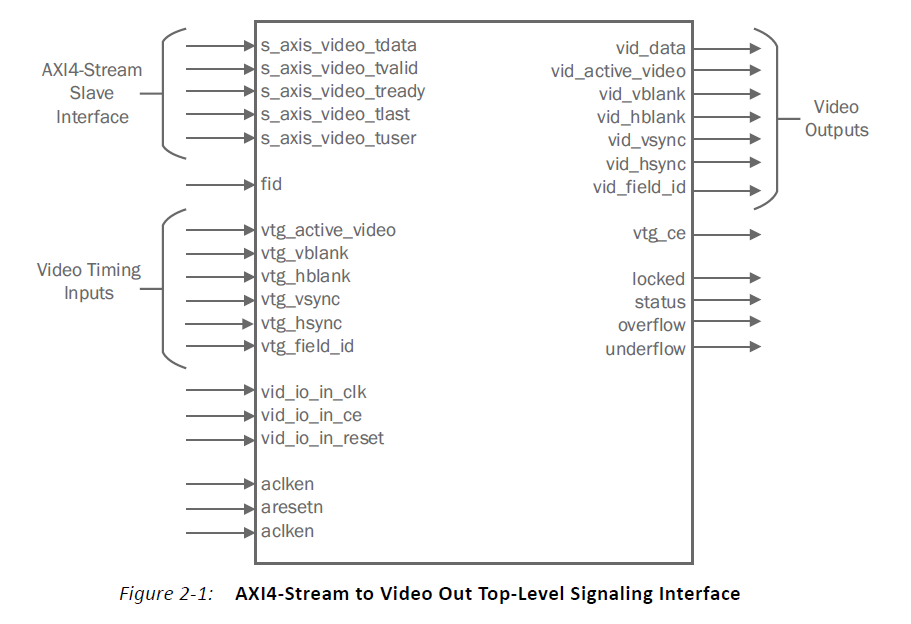

入出力信号とブロック図を下に示す。

| 信号名 | 方向 | バス幅 | 説明 |

|---|---|---|---|

| vid_io_out_clk | in | 1 | ピクセルクロック |

| vid_io_out_ce | in | 1 | ピクセルクロックのイネーブル信号 ・Lowにするとvtg_ce信号もLowになる。 |

| aclken | in | 1 | AXI4-Stream I/F のイネーブル信号 ・High:有効 ・Low :無効 |

| aclk | in | 1 | AXI4-Stream I/F のクロック |

| aresetn | in | 1 | AXI4-Stream I/F のリセット信号 ・ローアクティブ |

| vtg_ce | out | 1 | VTCクロックイネーブル信号 |

| fid | in | 1 | AXI4-StreamバスのフィールドID ・0=even field ・1=odd field |

| vid_io_out_reset | in | 1 | リセット信号、ハイアクティブ ・Independent clock modeのときのみ使用可能 |

| locked | out | 1 | VTCのロック信号 ・アンロック時:0・ロック時:1 ・ロック時、タイミング信号とビデオ信号が出力 |

| overflow | out | 1 | FIFOがアンダーフローしたことを示すフラグ |

| underflow | out | 1 | FIFOがオーバーフローしたことを示すフラグ |

| status | out | 32 | VTCの遅延とステートマシンの状態をモニタする信号 ・デバック時に使用する |

| video_in | in | - | スレーブAXI4-Stream I/F |

| vtiming_in^※2^ | in | - | VTCのタイミング信号 ・vtg_vsync ・vtg_hsync ・vtg_vblank ・vtg_hblank ・vtg_act_vid ・vtg_field_id |

| vid_io_outr^※3^ | out | - | ビデオ信号 ・vid_active_video ・vid_vsync ・vid_hsync ・vid_vblank ・vid_hblank ・vid_data ・vid_field_id |

| s_axis_video_tvalid | in | 1 | 有効なデータであることを示す信号 |

| s_axis_video_tuser^※1^ | in | 1 | ビデオフレームの先頭を示す信号 ・SOF信号とも呼ぶ |

| s_axis_video_tlast^※1^ | in | 1 | ビデオフレームの最後を示す信号 ・EOF信号とも呼ぶ |

| s_axis_video_tready^※1^ | out | 1 | FIFOのalmost full 信号 |

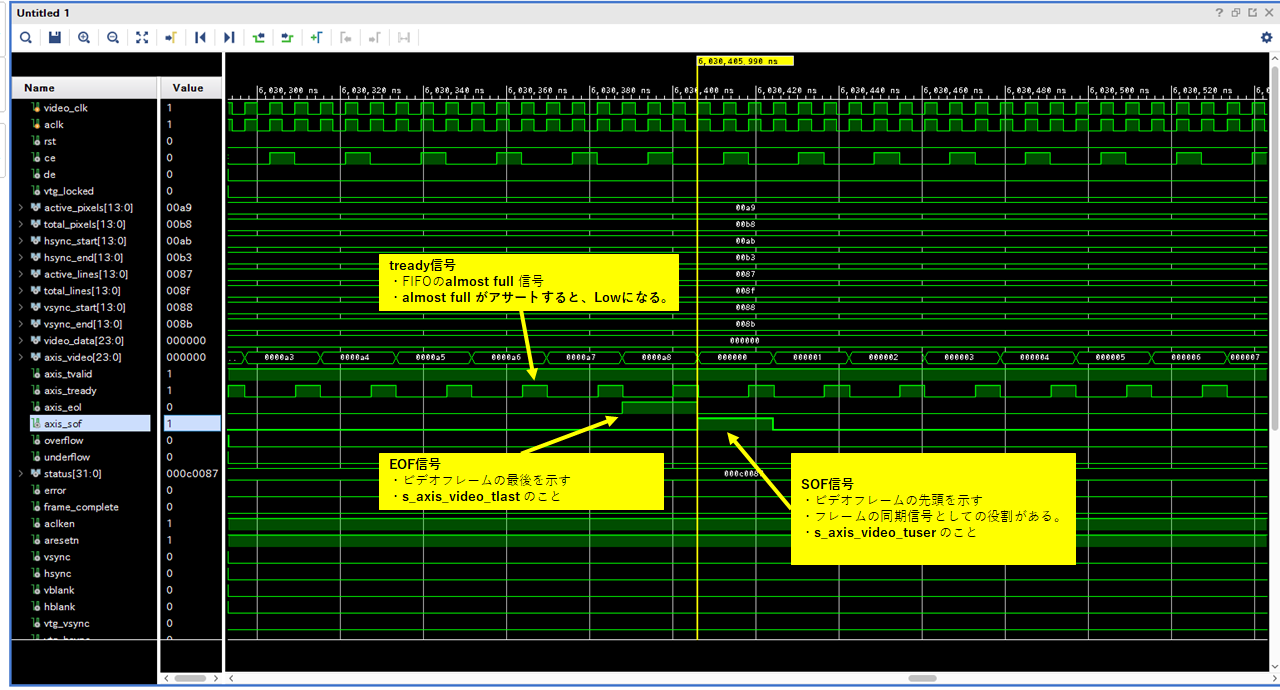

- ※1 :役立つか分からないが、自分の備忘録としてtuser、tlast、tready信号の波形を貼っておく。

※2 :Video Timing Controllerのタイミング信号はすべて出力させた方が良いらしい。また、Video Timing ControllerとAXI4-Stream I/Fの設定は、一致させないといけないらしい。

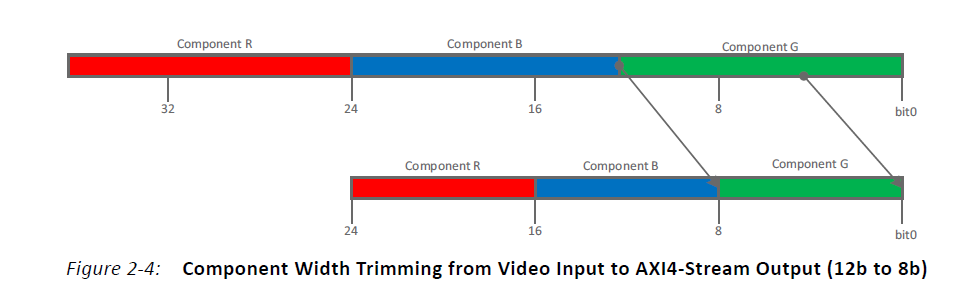

※3 :ビデオ信号「vid_data」の格納データは、下図に示すように、LSBから順番にGreen、Blue、Redとなっている。

構成

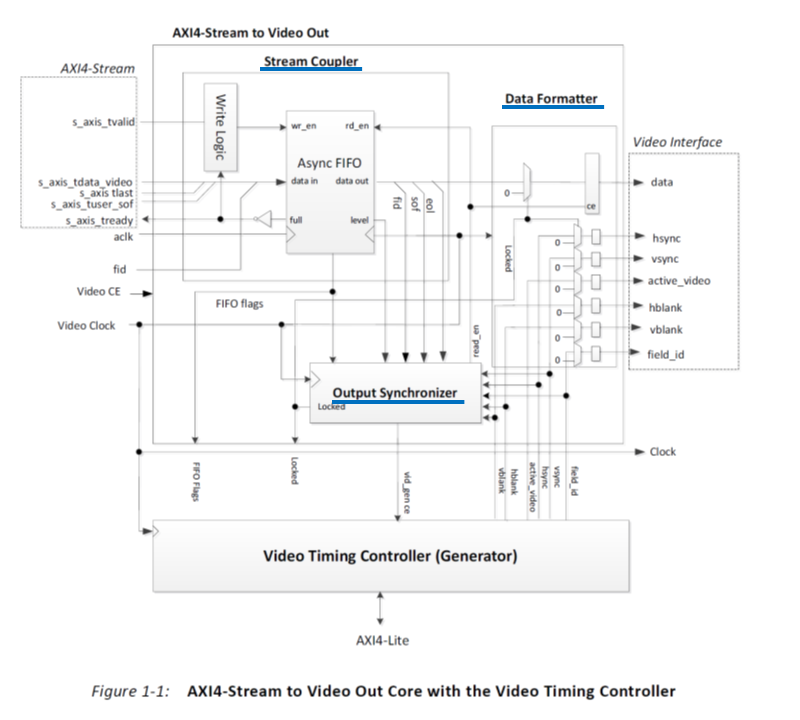

AXI4-Stream to Video Output は下図に示すように3つのブロックから構成されている。これらの概要や入出力信号について説明する。

Data Formatter

Data Formatterはビデオ信号のI/Fを生成するブロック。

ロック信号がLow (VTCからタイミング信号と入力データのタイミングが一致していない)のとき、ビデオ信号とタイミング信号はすべて出力をOFFする。ロック信号がHigh になり、vblank信号の立ち上がりのタイミングで、ビデオ信号とタイミング信号が出力される。

疑問点

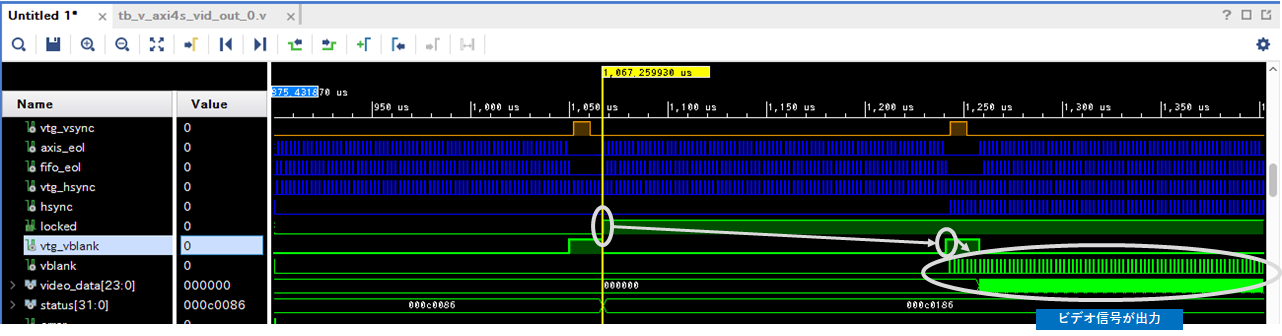

vblank信号とビデオ信号の出力タイミングの関係を表したシミュレーションの結果を下図に示す。シミュレーション結果を見るとvblank信号が8サイクル後に、ビデオ信号が出力されている。

てっきり、vblank信号が出力後すぐにビデオ信号が出力されるのだと思ったのだが、違うようだ。その理由が分かったら追記する。

Stream Coupler

Stream Couplerは、クロック載せ替え回路とバッファリングの役割を担うブロック。このブロックは、非同期FIFOとFIFOの入力側に配置している書き込みロジックにより構成されている。

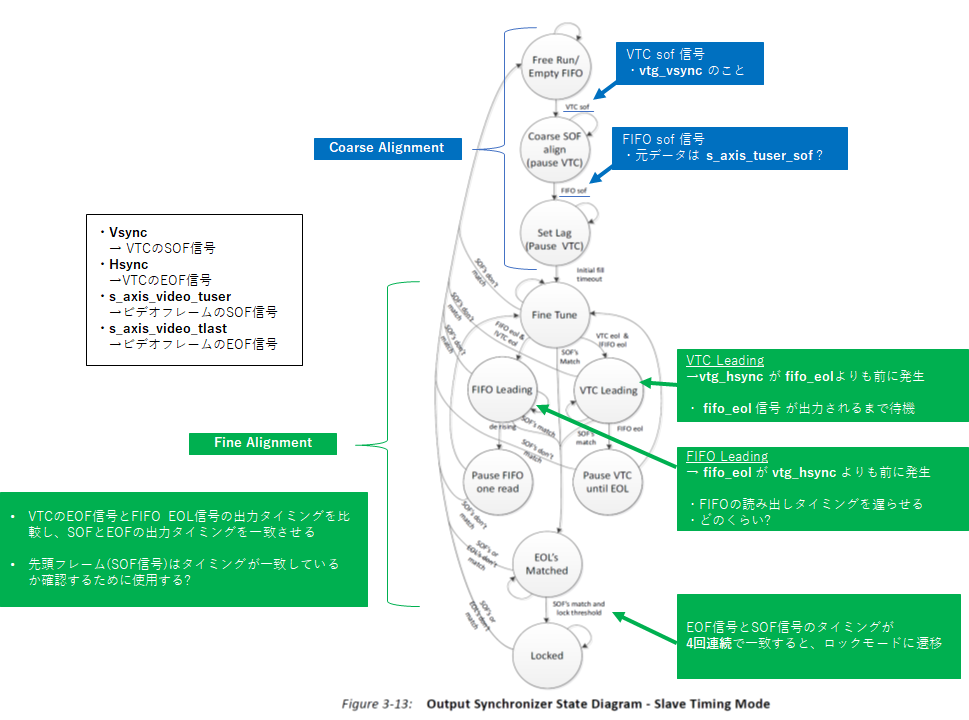

Output Synchronizer

Output Synchronizerは、入力データとVTCからのタイミング信号の同期をとる役割を担うブロック。同期をとるための制御フローを下に示す。入力データとタイミング信号の同期は、Coarse AlignmentとFine Alignmentを行うことで実現する。

制御フローは、モードの設定によって異なる。モードは、スレーブモードとマスターモードの2種類存在する。上記の制御フローはスレーブモード時のものである。

- スレーブモード :VTCからのタイミング信号とSOF信号・EOF信号を比較し、入力データとタイミング信号の出力タイミングを一致させる。

- マスターモード :EOF信号のみを使用して、入力データとタイミング信号の出力タイミングを一致させる。

※データシートを見ると、Slave モードを推奨しているようだ。

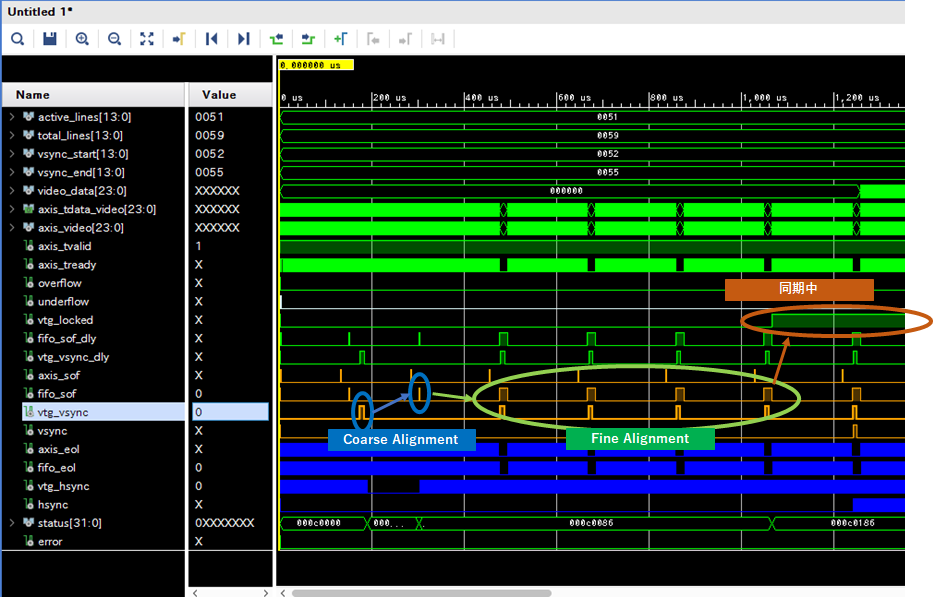

シミュレーション結果を下図に示す。データシートと上記の制御フローに記載されている通りの動作が行われている。

疑問点

使用したシミュレーションモデルは、マスターモードなのかスレーブモードなのかわかっていない。シミュレーションモデルのDUTのソースコードを見ると、

C_VTG_MASTER_SLAVE = "0"となっていたので、おそらくスレーブモード?。使用したシミュレーションモデルは、Fine Alignment時にSOF信号とEOF信号のタイミングが4回連続で一致している。そのため、制御フローにある「VTC Leading」や「FIFO Leading」の動作は見られなかった。これらの動作時はどうなっているか分かったら追記する。

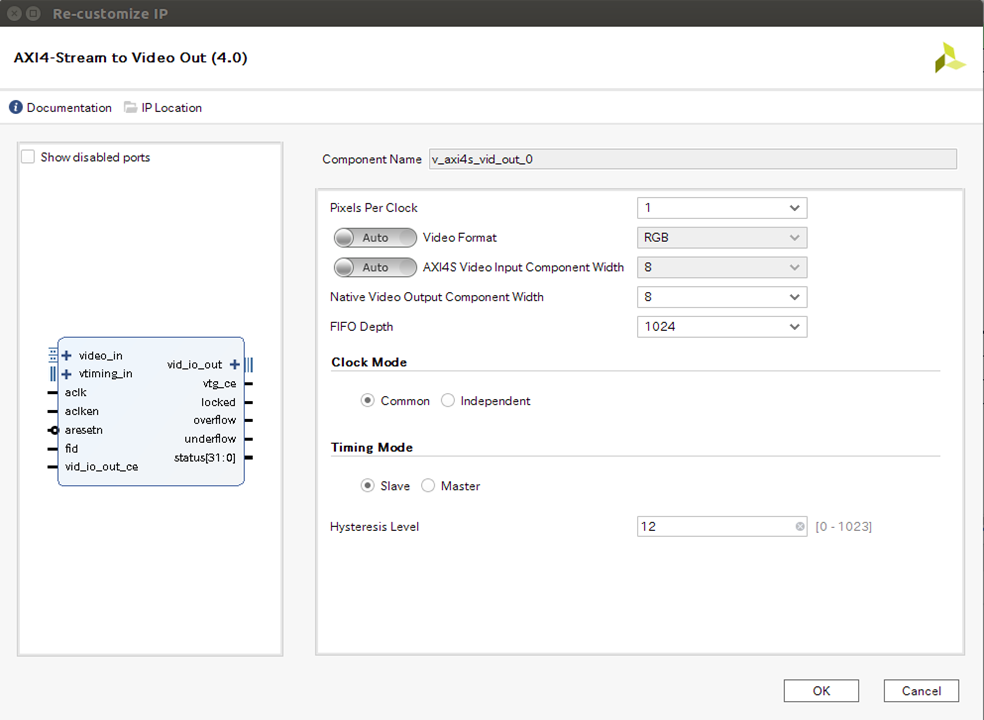

設定項目

このIPは、下図に示すように設定項目がある。これらについて説明する。

Pixels Per Clock

出力するピクセル数を選択する。この設定により、ビデオ信号のバス幅が変化する。選択項目は次の中から選択する。

- 選択:1、2、4

Video Format

使用するビデオ信号のフォーマットを選択する。Autoを選択すると、入力ビデオ信号のビデオフォーマットに基づき、使用するビデオ信号のフォーマットが選択される。この設定により、ビデオ信号のバス幅が変化する。なお、ビデオ信号のバス幅は次の計算式から求められる。

AXI4S Vudeo Input Component Width

AXI4-Streamにより入力されるビデオ信号の各bit幅のこと。ManualとAutoで選択可能。Manualの場合は、次の中から選択する。

Native Video Output Component Width

出力するビデオ信号の各bit幅のこと

Clock モード

common モードと independent モードがある。

commonモード

commonモードは、video_inとvid_io_outが共通の同期クロックで動作している場合に使用する。このモードは、内部FIFOにあるクロック乗せ換え回路を使用しないため、リソースが節約できる。

independent モード

independent モードは、video_inとvid_io_outが非同期クロックで動作している場合に使用する。

aclkはvid_io_out_clkと同じかそれ以上の周波数であること。aclkがvid_io_out_clkよりも遅い場合、バッファリングが必要である。

Timing モード

Slave モードと Masterがある。これらの違いは、上記のOutput Synchronizerにて記載している。

Hysteresis Level

フレームバッファの「クッションレベル?」を定義するらしい。推奨する設定値は12~16の間。なお、FIFOの深さは次の式により決まるようだ。

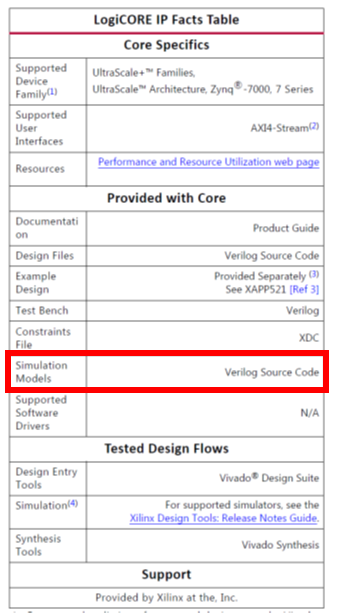

シミュレーションモデル

このIPコアには、下図に示すようにシミュレーションモデルが存在する。上記で示したいくつかのシミュレーション結果は、このシミュレーションモデルを使用したものである。

初めてシミュレーションモデルがあることに気が付いた。シミュレーションモデルの使い方は別の記事で説明する。

おわりに

データシートを読んで半分くらい理解できた気がする。残りは実際に設計したときに理解できるようにしたい。

関連資料

- AXI4-Stream to Video Out v4.0

https://japan.xilinx.com/support/documentation/ip_documentation/v_axi4s_vid_out/v4_0/pg044_v_axis_vid_out.pdf - Video Beginner Series 8: Debugging the AXI4-Stream to Video Out IP

https://forums.xilinx.com/t5/Video/Video-Beginner-Series-8-Debugging-the-AXI4-Stream-to-Video-Out/td-p/866346