ADC IPの作成

AD変換機能

MCP3002をFPGAで動かすためにIPコアを作った。これはその時のメモである。

MCP3002の仕様

- 分解能 :10 Bit

- 変換方式 :SAR

- 変換レート:200 ksps @VDD=5V

- チャンネル:2

ADC IPの仕様

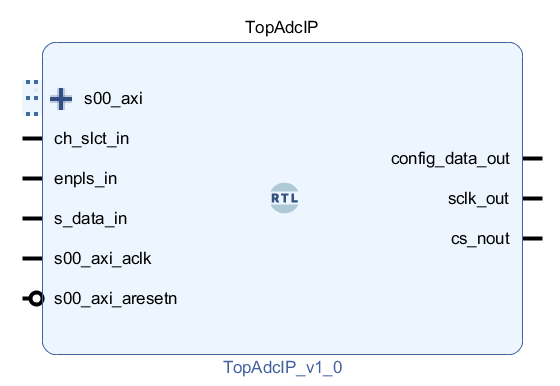

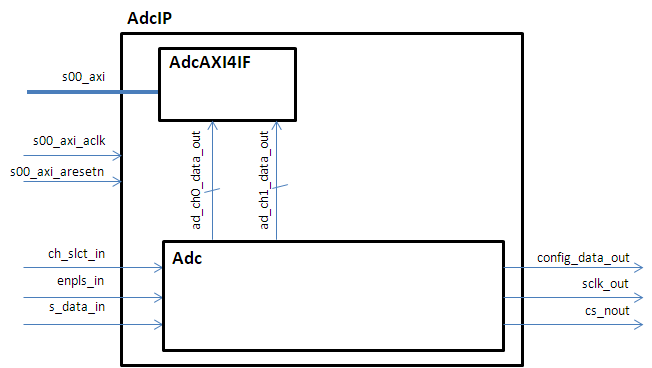

ブロック図

信号表

| 信号名 | 方向 | bit幅 | 論理 | 説明 | 備考 |

|---|---|---|---|---|---|

| s00_axi | 32 | AXI4-Liteスレーブ | |||

| s00_axi_aclk | in | 1 | 正 | クロック、100MHz | |

| s00_axi_aresetn | in | 1 | 負 | リセット信号 | |

| ch_slct_in | in | 1 | 正 | ADのCH選択 ・1'b0→CH0 ・1'b1→CH1 |

|

| enpls_in | in | 1 | 正 | AD変換開始トリガ信号 ※パルス入力 |

|

| s_data_in | in | 1 | 正 | ADシリアルデータ | ADC IC接続 |

| config_data_out | out | 1 | 正 | ADC設定データ | ADC IC接続 |

| sclk_out | out | 1 | 正 | ADC用クロック信号 | ADC IC接続 |

| cs_nout | out | 1 | 正 | チップセレクト信号 | ADC IC接続 |

構成

ディレクトリ

TopAdcIP

├AdcAXI4IF

└Adc

テストベンチ

- SimAdc.v

構成図

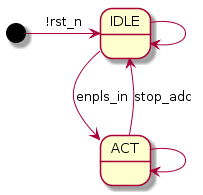

状態遷移

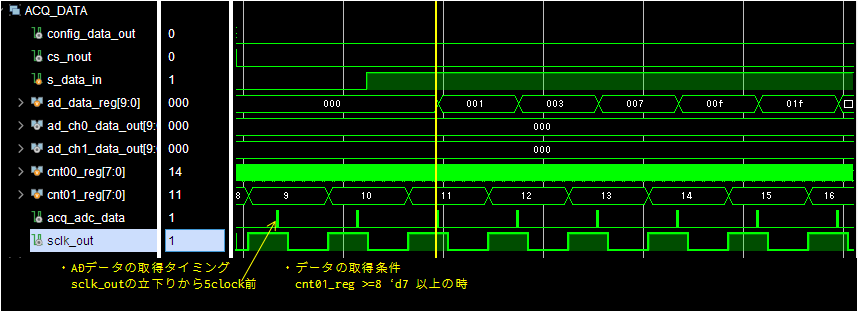

//カウント値 parameter OFFSET_CNT00=8'd19; parameter CNT00_MAX=8'd39; parameter CNT01_MAX=8'd16; //---reg & wire ---// wire match_cnt01 =(cnt01_reg >=CNT01_MAX); wire stop_adc =(cnt00_reg >=CNT00_MAX-1 && match_cnt01);

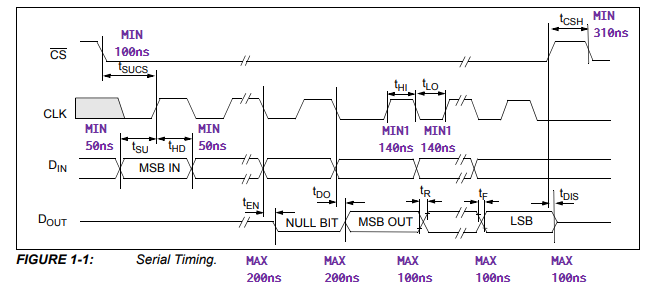

タイミングチャート

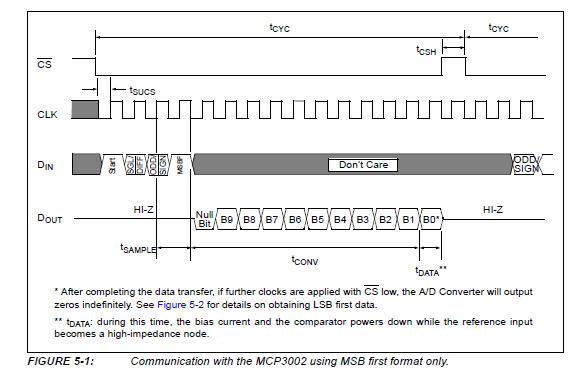

MCP3002

- タイミング規定

- MSBファーストのタイミングチャート

- MSBファーストのタイミングチャート

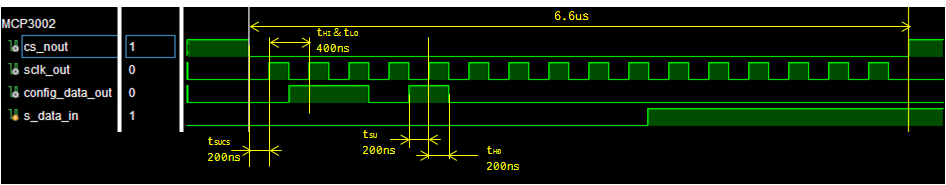

AdcIP

- 外部インターフェース

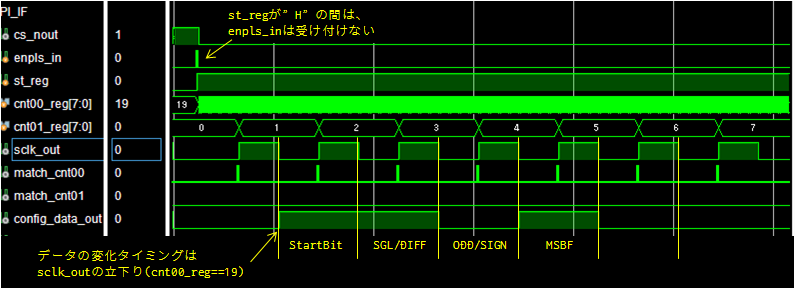

- ADC設定データ

図 AcdIPの設定データ波形と出力タイミング

表 設定データ一覧

| SCLK Cycle | config_data_out | 設定値 | 説明 |

|---|---|---|---|

| 1 | 0 | なし | |

| 2 | 1 | Start bit | |

| 3 | 1 | SGL/DIFF | シングルエンド出力 |

| 4 | 1/0 | ODD/SIGN | CH選択 ・1'b0→CH0 ・1'b1→CH1 |

| 5 | 1 | MSBF | ・1'b0→LSBファースト ・1'b1→MSBファースト |

| 6~16 | 0 | なし |

- ADデータ取得タイミング

LSBについて

今回の回路はVREF3.3Vなので、

1LSB= VREF / 10bit

= 3.3(V)/ 1024

= 3.22(mV)